集成电路对讲机 电路图解析与集成电路设计探析

对讲机作为一种重要的近距离双向通信工具,其核心已经从早期的分立元件逐步演进为高度集成的集成电路(IC)方案。集成电路设计不仅极大地缩小了对讲机的体积、降低了功耗,还显著提升了其稳定性和功能丰富性。本文将从电路图解析入手,深入探讨对讲机中集成电路的设计原理与关键技术。

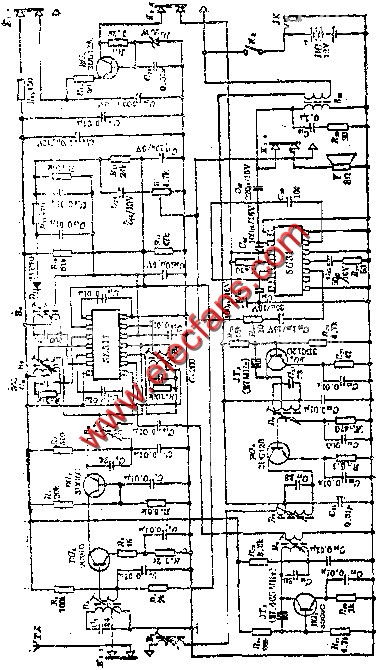

一、 经典集成电路对讲机电路图核心模块解析

一套完整的对讲机电路系统,其核心通常由一块或几块专用集成电路构成。一个典型的单工调频(FM)对讲机电路图主要包含以下几个由IC实现的核心模块:

- 射频收发模块:这是对讲机的“心脏”。现代对讲机通常采用一颗集成了锁相环(PLL)频率合成器、压控振荡器(VCO)、混频器、中频放大器甚至功率放大器(PA)的射频IC。在电路图中,它连接着晶体振荡器、环路滤波器、天线开关等外围元件,共同完成载波频率的精准生成、信号的调制与解调。

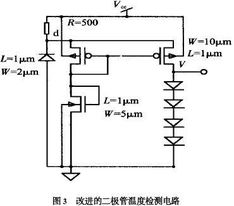

- 基带/音频处理模块:负责语音信号的加工。发射时,麦克风拾取的微弱音频信号经过运算放大器IC构成的预放电路后,送入调制器;接收时,从中频IC解调出的音频信号,需经过由音频功率放大器IC驱动的扬声器还原为声音。静噪电路、音频滤波等也常由运放IC实现。

- 微控制器(MCU)模块:在智能对讲机中,一颗MCU是控制中枢。它在电路图中连接着键盘、液晶显示屏(LCD)、频道选择开关、PTT(按键通话)键等。MCU通过编程,管理着频率设定、信道扫描、电池监测、数字信令(如CTCSS/DCS亚音编解码)等所有逻辑与控制功能。

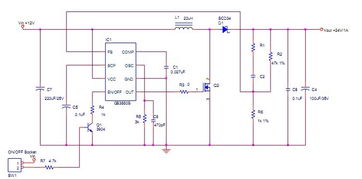

- 电源管理模块:由低压差线性稳压器(LDO)IC或开关稳压器IC构成,为射频、基带和MCU等不同模块提供稳定、纯净且不同电压等级的电源,确保系统高效、可靠工作。

通过分析电路图,可以清晰地看到各IC之间的信号流向、电源分配及控制关系,这是理解对讲机工作原理和进行故障排查的基础。

二、 对讲机专用集成电路的设计考量与挑战

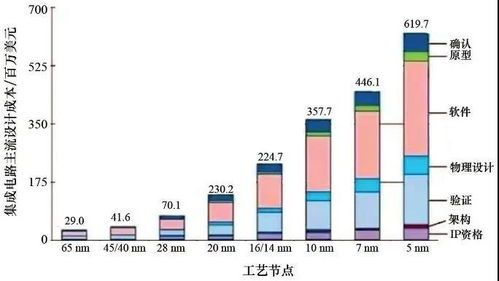

设计一款用于对讲机的集成电路,工程师需要综合考虑性能、功耗、成本与集成度,面临多方面的技术挑战:

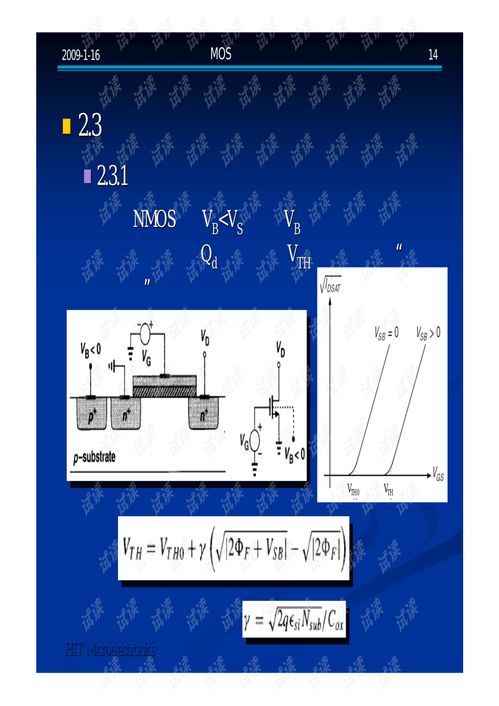

- 射频性能优化:射频IC的设计是重中之重。需要在特定频段(如VHF 136-174 MHz, UHF 400-470 MHz)实现低相位噪声的频率合成、高线性度的功率放大以及高灵敏度的低噪声放大。这涉及到深亚微米射频CMOS或SiGe BiCMOS工艺的选择、片上电感与变压器的优化设计,以在芯片面积和性能间取得平衡。

- 低功耗设计:对讲机通常由电池供电,续航能力是关键。设计时需采用多电源域、时钟门控、电源关断等动态功耗管理技术。特别是在接收待机状态,要使大部分电路处于极低功耗的“睡眠”模式,仅维持必要功能的运行。

- 高集成度与系统级封装(SiP):为了追求极致的体积与成本优势,趋势是将射频收发、基带处理甚至MCU内核集成到单颗芯片上,即“单片对讲机解决方案”。数字电路与敏感的模拟射频电路集成会带来严重的噪声耦合问题。因此,精心的版图布局、电源地隔离、衬底噪声抑制技术至关重要。作为替代或补充,采用SiP技术将多颗不同工艺的裸芯片封装在一起,也是实现高性能、小型化的有效途径。

- 可靠性与稳定性:对讲机工作环境复杂,IC必须具有良好的抗静电(ESD)能力、宽工作温度范围以及稳定的频率特性。在电路设计中需要加入完善的保护电路,并在制造工艺上予以保证。

- 支持灵活的可编程性:为了适应全球不同地区的频率规划与通信标准,现代对讲机IC往往设计成可通过MCU软件灵活配置频率、调制偏差、亚音码等参数,这要求IC内部有相应的可编程寄存器接口(如SPI、I2C)。

三、 未来发展趋势

随着物联网和专用移动无线电的发展,对讲机集成电路正朝着软件定义无线电(SDR)方向演进。未来的对讲机核心芯片可能是一个高度可编程的射频前端配合一个强大的数字信号处理器(DSP),通过软件实现波形、协议和功能的动态重构,从而实现更宽的频带覆盖、更强的抗干扰能力和更丰富的增值服务。

一张简洁的对讲机电路图背后,凝聚着精密的集成电路设计智慧。从模块解析到芯片设计,每一步都体现了在有限资源下对通信性能、功耗与成本的不懈追求。理解这些,不仅能更好地应用和维护对讲机设备,也为通信电子产品的创新设计提供了宝贵的思路。

如若转载,请注明出处:http://www.xjioter.com/product/23.html

更新时间:2026-04-26 21:19:54